## OVERVIEW OF DIGITAL SIGNAL PROCESSING SYSTEMS AT GMRT

## B. Ajith Kumar

#### Group Head : GMRT Back-end Systems

#### **ARDRA - 2019**

Lonavala, Maharashtra November 15, 2019

## **Team Members**

- Harshwardhan Reddy : Signal processing, GPU backends

- Kaushal Buch

- Sandeep Choudari

- Mekhala Muley

- GJ Shelton

- Sanjay Kudale

- Irappa Halagalli

- Navnath Shinde

- Sweta Gupta

- : RFI Filtering, Beamformer for FPAs

- : FPGA backends, Walsh scheme

- : FPGA based signal processing

- : Computing and Networking Hardware

- : Data Acquisition, Programming

- : Backend system integration & Tests

- : Time & Frequency Standards

- : Analog Signal Processing

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## **Upgraded GMRT**

## **Hybrid Digital Backends**

Nove 15, 2019Overview of Digital Signal Processing Systems at GMRT3 of 32

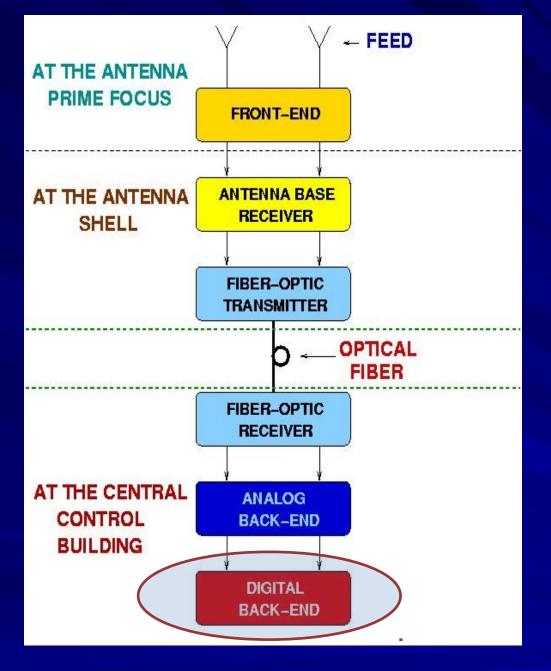

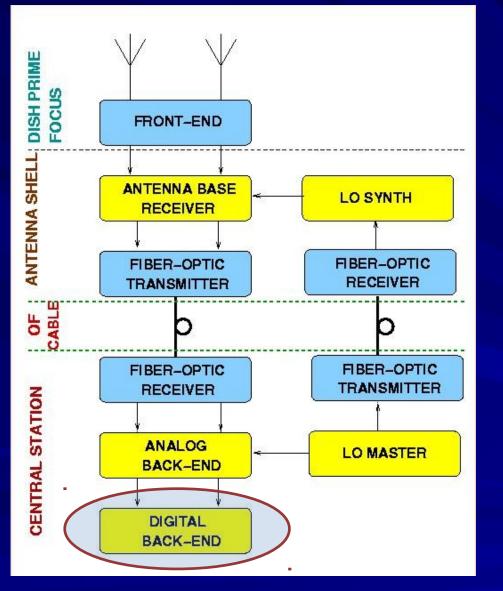

# **uGMRT** Receiver

GMRT Operating Freq : 100 to 1500 MHz

Instantaneous Bandwidth : 400 MHz (max)

Real-time Backend processing to generate Visibility & Beam outputs

Nove 15, 2019Overview of Digital Signal Processing Systems at GMRT4 of 32

## uGMRT Backend Specifications

- Number of stations

- Number of input polarizations

- Max instantaneous BW

- Number of spectral channels

- Full Stokes capability

- Dump time

- Sub-array support

- Narrowband modes

- Number of Beams

- : 32

- : 2

- : 400 MHz

- : 2048 16384

- : Yes

- : 671 ms

- : Yes

- : Yes (min resolution 95 Hz)

- : 4 (IA or PA or Voltage)

(max 1 Voltage beam @ 200 Mhz BW)

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 5 of 32

## Design

## **GWB** : Compute Requirements

| Bandwidth             | 400 MHz           |

|-----------------------|-------------------|

| FFT                   | 3.1 Tflops (16K)  |

| Phase Shifter         | 100 GFlops        |

| Multiply & Accumulate | 6.4 TFlops        |

| Beamformer            | 150 Gflops / beam |

| Total                 | 10 TFlops         |

#### I/O Data rate :

Input : FPGA board to Compute Node = 12.8 Gbps Sharing : Compute nodes = 12 Gbps (bidirectional)

Visibility Output = 3.2 Gbps (16K spectral channels Total Intensity) Beam Output = 1.6 Gbps (PA Total Intensity at 20 uS) Voltage beam Output = 6.4 Gbps

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 7 of 32

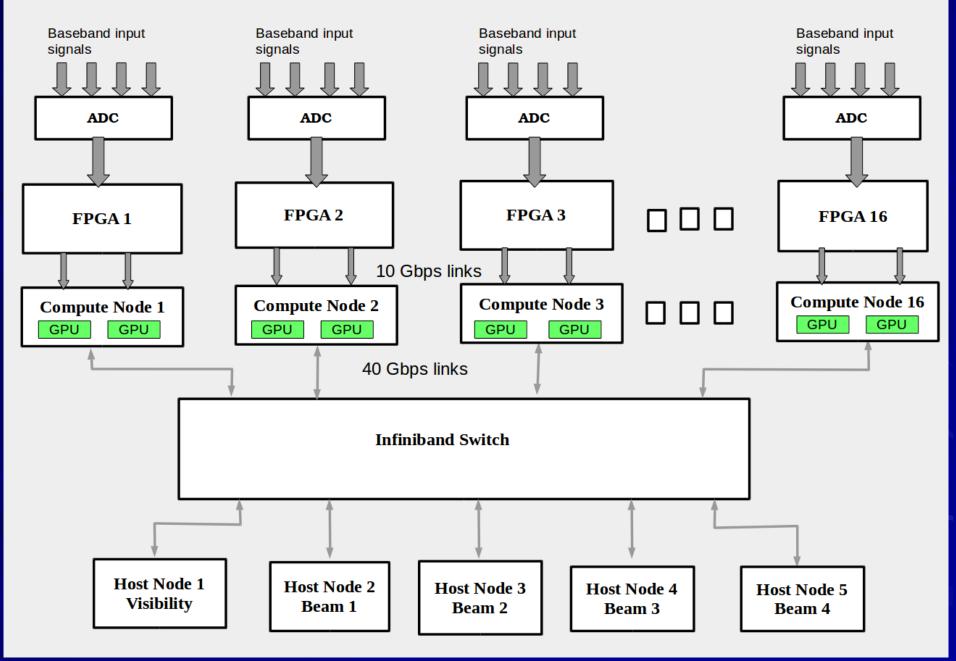

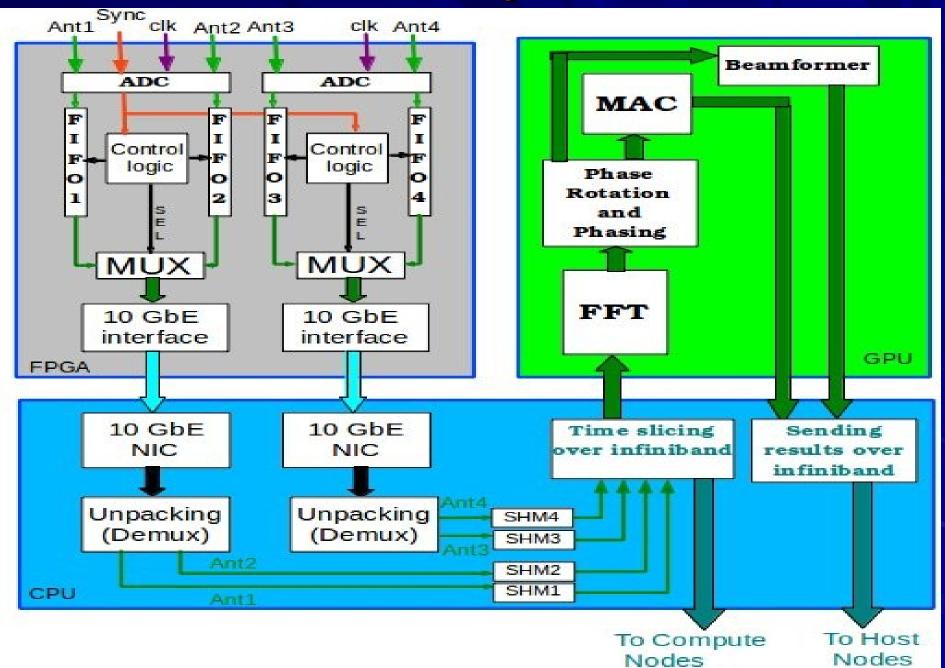

## **Data Flow in single FPGA-GPU**

## **Hardware Implementation**

16 ROACH (FPGA) boards with Atmel/e2v based ADCs developed by CASPER group for digitization & packetization

16 Dell T630 machines as Compute Nodes

32 Tesla K40c GPU cards for processing

Dell servers as Hosts : Visibility-1, Beam-4

36 port Mellanox Infiniband switch for data sharing between Compute Nodes and Host Nodes

Developed in collaboration with Swinburne University, Australia

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 9 of 32

## **GMRT Backends : Hardware Components**

CASPER design ADC board (iADC) ADC Chip : Atmel/e2v 8-bit Dual ADC Max. clock : 1.2 GSps Analog BW : 1.5 GHz

CASPER design FPGA Virtex 5 boards RAM : 512 MB DDR2 AMCC PowerPC 2 Z-DOK connectors 4 CX4 10Gbps conn.

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## **GMRT Backends : Hardware Components**

#### Compute node Dell T630

| Processors                     | : 2 x Intel Xeon E5-2600 v4 |  |

|--------------------------------|-----------------------------|--|

| RAM                            | : 64 GB DDR4 DIMMs          |  |

| Drive Bays                     | : 32 x 2.5" or 18 x 3.5"    |  |

| PCIe slots                     | : X 8 slots                 |  |

| GPU Support                    | : Four GPUs 300W            |  |

| Embedded NIC : Dual port 1 GbE |                             |  |

|                                |                             |  |

| <u>GPU : nVidia K40</u>             |             |  |

|-------------------------------------|-------------|--|

| No. of cores                        | : 2880      |  |

| Global memory                       | : 12 GB     |  |

| Memory bandwidth                    | : 288 GB/s  |  |

| Board Power                         | : ~235 Watt |  |

| No. of Multiprocessors : 15         |             |  |

| Peak performance (SP) : 4.29 Tflops |             |  |

| Peak Performance (DP) : 1.43 Tflops |             |  |

|                                     |             |  |

Nove 15, 2019Overview of Digital Signal Processing Systems at GMRT11 of 32

## **GMRT Backend implementation**

Compute Nodes

#### Host Nodes

*Nove* 15, 2019

Overview of Digital Signal Processing Systems at GMRT

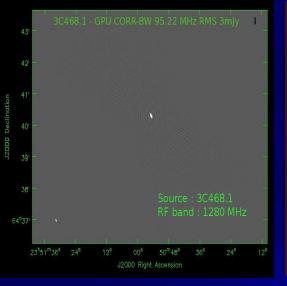

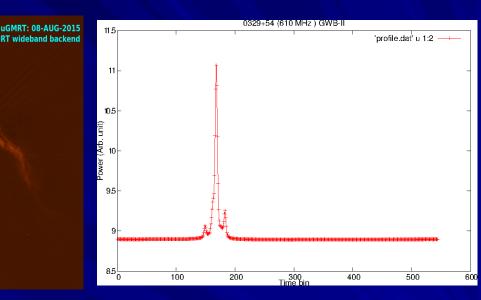

# **Typical Results - uGMRT**

uGMRT: 08-AUG-2015

300-500 MHz frequency band

GMRT wideband backend

14 antennae, dual polarisation

integration time = 6 times 30 min

rms noise = 0.2 mJy/beam (6.4" resolution)

First image using GWB Source 3C468 L-band, 100 MHz BW RMS noise – 3 mJy

Source : 3C129 14 antennas, 300-500MHz Bandwidth : 200MHz Pulsar : B0329+54 8 antennas, IA mode RF : 610 MHz

#### *Image Courtesy : DV Lal & Others*

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 13 of 32

## **GWB** Current developments

- User host for data access by Telescope user during observation

- Implementation of PFB for channelisation & narrow band modes

- Parallel Backend System GPB for raw voltage record + process

- Tests on new servers and GPUs for next level update

- Prototype tests on Early digitisation at Antenna site

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 14 of 32

## Software Backends

Nove 15, 2019Overview of Digital Signal Processing Systems at GMRT15 of 32

## **GMRT Receiver**

GMRT Operating Freq : 100 to 1500 MHz

Instantaneous Bandwidth : 32 MHz (max)

Real-time Backend processing to generate Visibility & Beam outputs

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

# **GSB** specifications

- Number of stations

- Number of input polarizations

- Max instantaneous BW

- Number of spectral channels

- Full Stokes capability

- Dump time

- Sub-array support

- Narrowband modes

- Number of Beams

- Raw voltage recording

- : 32

- : 2

- : 32 MHz

- : 512

- : Yes

- : 2 s

- : Yes

- : Yes

- : 2 (IA or PA or Voltage)

- : 16 Mhz, 4 bits/sample

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

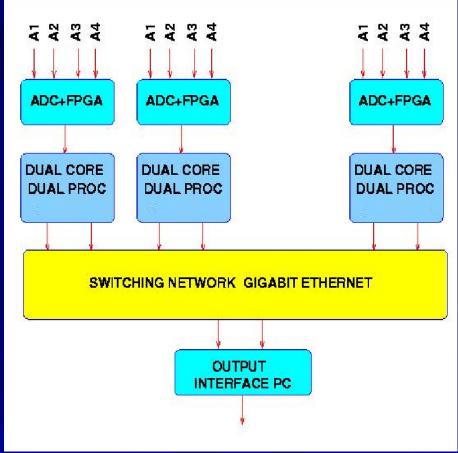

# Software Back-end

- Digitisation on ADC boards

- Analog signal : 16/32 MHz BW

- ADC to CPU via interrupt driven DMA

- Distribute data to each node time slice

- Delay, FFT, Fringe stop, MAC at node

- Record integrated visibilities results

<u>ACQ Nodes</u> : Dual core, Dual processor Intel Xeon CPUs With 8-bit, 4 Channel, 66 MSPS, PCI-X compliant ADC card <u>Compute Nodes</u> : Quad core, Dual processor Intel Xeon CPUs <u>Recording Nodes</u> : Dual core, Dual processor Intel Xeon CPUs **Number of Nodes required = 48**

Details from Report : J.Roy+othersNove 15, 2019Overview of Digital Signal Processing Systems at GMRT18 of 32

# Software Back-end Implementation

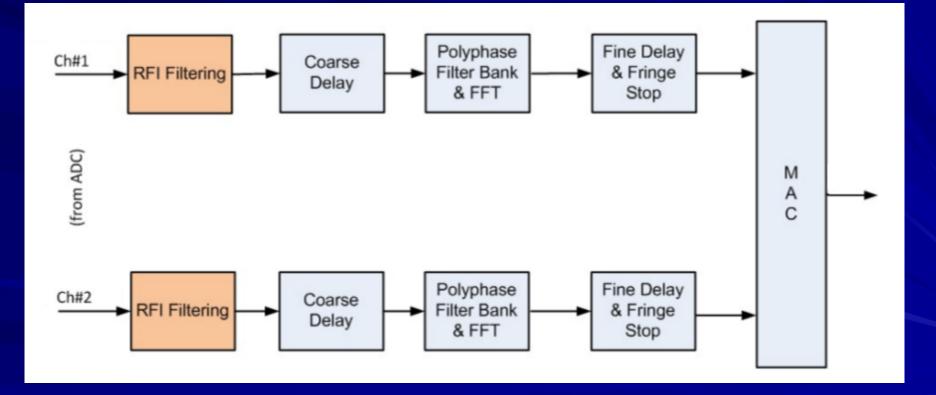

## **Other CASPER based designs**

- Packetised Correlator

Packetised Beamformer

- Pocket Correlator Pocket Beamformer

- Design Blocks

- 32 mtr dish Backend

- 15 mtr dish Backend

- Digital Noise Generator

- : 8 ant, 2 pols, BW 400MHz (Using iADC+Roach boards)

- : 2 ant, 2 pol, BW 400MHz (Single Roach board)

- : Coarse Delay Fine Delay + Fringe Stop Gaussian Random number gen Impulsive RFI Excision

: 2 pols, self & Raw-data (Single iADC+Roach)

: 2 pols, self & Radata

- (Single iADC+Roach)

- : 2 outputs with variable corr (Single Roach Board)

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## **Recent Developments**

Nove 15, 2019Overview of Digital Signal Processing Systems at GMRT21 of 32

# **RFI Mitigation for GWB**

Broadband RFI detection and cancellation scheme developed. The scheme uses the statistical properties of astronomical signal. Implemented in the digital backend on FPGA boards.

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## **Real-time RFI Detection and Filtering**

Median Absolute Deviation (MAD) is a robust measure of dispersion of data set. MAD = median (abs (Xi - median(X)))Standard Deviation = 1.4826 X MAD Threshold = [median  $\pm n*\sigma MAD$ ]

Real-time calculation of Standard Deviation of data set.RFI detection by comparing with Threshold.Filtering options - replacement with1. Constant value2. Digital noise3. Threshold

To take care of longer bursts of RFI, Median of MAD (MoM) is used, Median of MAD (MoM) = M(D1, D2, ...., Dn)

The current design uses 16k MoM – i.e. median of 16k MAD values. RFI counter keeps record of number of detected RFI samples and total samples.

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT 23 of 32

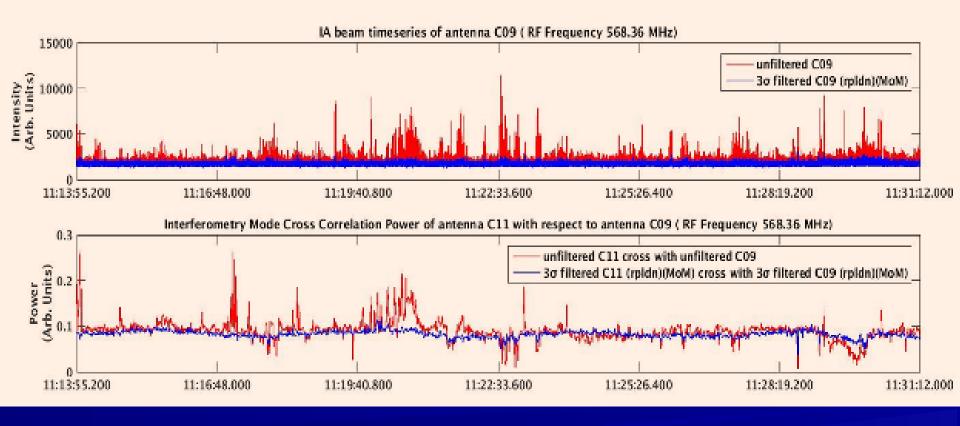

## **Test Results – RFI Filtering**

Effect of RFI filtering on Beam output and visibility output

Tested using two closely spaced antennas, C9, C11

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

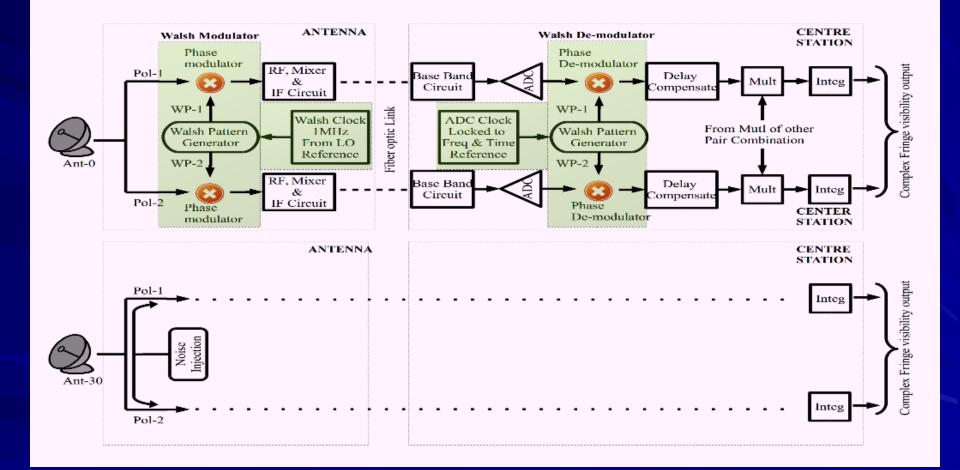

## **Walsh Scheme for GMRT**

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## Walsh modulation scheme

- 128 bit Walsh pattern used at GMRT

- •64 unique patterns for Phase modulation of RF signal at antenna

- •CPLD based circuit at antenna base for pattern generation

- Sequency Pulse to indicate first bit of Walsh pattern

- Sequency transmitted to central station over return link

- •Walsh regenerated at central station in FPGA for demodulation

- Walsh demodulation implemented in Roach board

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

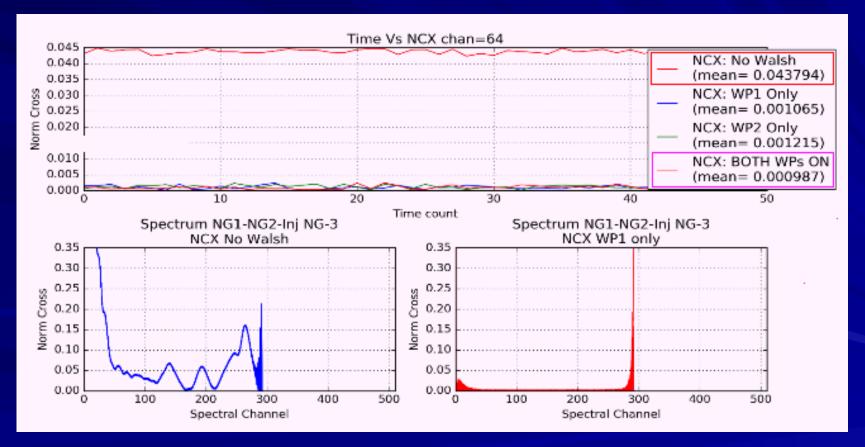

# **Results : Cross Talk rejection**

- Measured by injecting a common noise to two inputs of GWB

- With no Walsh applied shows a cross corr value of 0.044

- With Walsh in one or both channels cross corr drops to 0.001

*Nove* 15, 2019

Overview of Digital Signal Processing Systems at GMRT

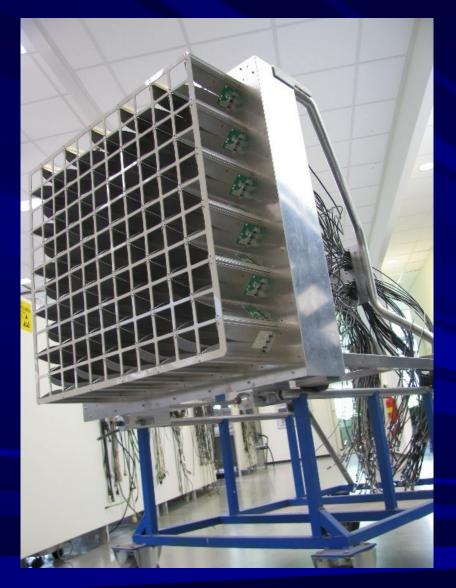

## **Multi-beam Beamformer for FPA**

# Focal Plane ArrayFrequency: 1100 to 1700 MHzNo. of Elements: 8 X 9 dual polVivaldi Elements: AluminiumElement spacing: 11 cm

FPA unit developed by Astron Tech Info Courtesy : Astron Documents

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

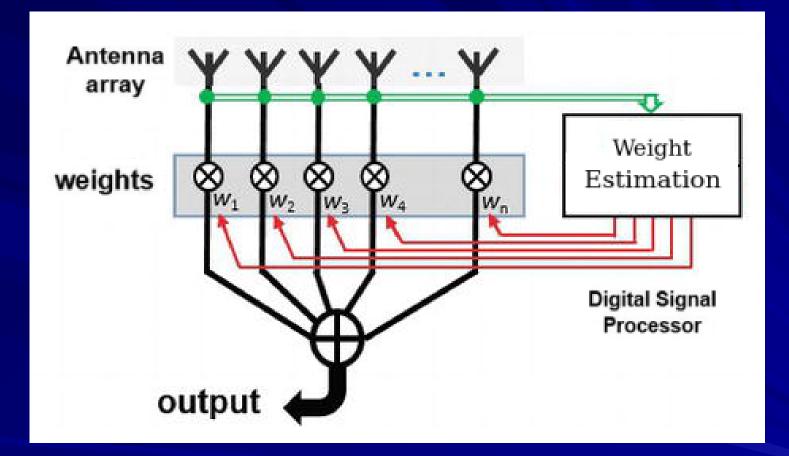

## **Beamformer**

Beamformer Hardware : 64-input, 12-bit ADC connected to ROACH board Narrowband multi-beam beamformer & correlator (max. 32 MHz bandwidth)

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

## **Beamformer - Implementation**

#### <u>Beamformer</u>

Bandwidth Beam former Freq resolution Phase scaling Amp scaling Integration time Beam power : 32 MHz

: 0.671 s

: 16 bits

: 16 inputs, 4 beams

n : 31.25 Khz, 1024 Ch

: 360 deg mapped to 2048

: 8 unsigned bits - 24 dB

30 of 32

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT

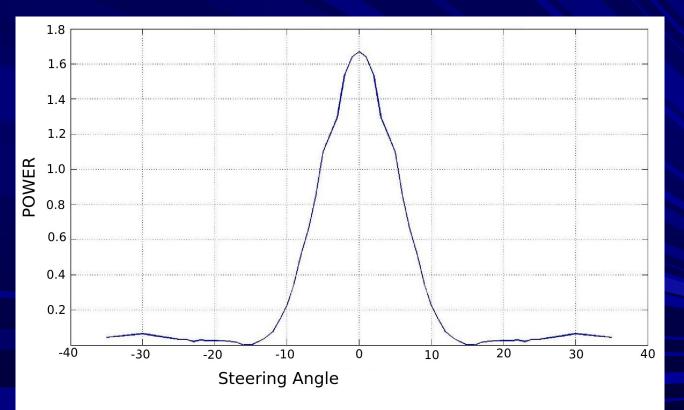

## **Beam Steering**

8 elements used for testing the Beam steering

A CW signal transmitted using the 3 mtr dish

Beam formed with appropriate weights applied to each element

The beam is steered in a vertical direction by changing the phase.

Nove 15, 2019 Overview of Digital Signal Processing Systems at GMRT